学术新闻

信息科学技术学院彭练矛-张志勇教授课题组在《科学》发表5nm碳纳米管CMOS器件研究成果

来源: 信息科学技术学院

集成电路发展的基本方式在于,在晶体管尺寸缩减的前提下,研制性能更强大、集成度更高、功能更复杂的芯片。目前,主流CMOS(互补金属氧化物半导体)技术将达到10 nm(纳米)的技术节点,后续由于受到来自物理规律和制造成本的限制而很难继续提升,“摩尔定律”可能面临终结。20多年来,科学界和产业界一直在探索各种新材料和新原理的晶体管技术,以期替代硅基CMOS技术,然而迄今为止,尚未实现10 nm新型CMOS器件,也没有新型器件能够在性能上真正超越最好的硅基CMOS器件。

碳纳米管被认为是构建亚10 nm晶体管的理想材料,其原子量级的管径保证器件具有优异的栅极静电控制能力,更容易克服短沟道效应;超高的载流子迁移率则保证器件具有更高的性能和更低的功耗。理论研究表明,碳管器件相对于硅基器件来说,在速度和功耗方面具有5~10倍的优势,有望满足“后摩尔时代”集成电路的发展需求。可是,2014年国际商用机器公司(IBM)所实现的最小碳管CMOS器件仅停滞在20 nm栅长,性能也远远低于预期。

北京大学信息科学技术学院、纳米器件物理与化学教育部重点实验室彭练矛-张志勇教授课题组在碳纳米管电子学领域进行了十多年的研究,发展了一整套高性能碳管CMOS晶体管的无掺杂制备方法,通过控制电极功函数来控制晶体管的极性。

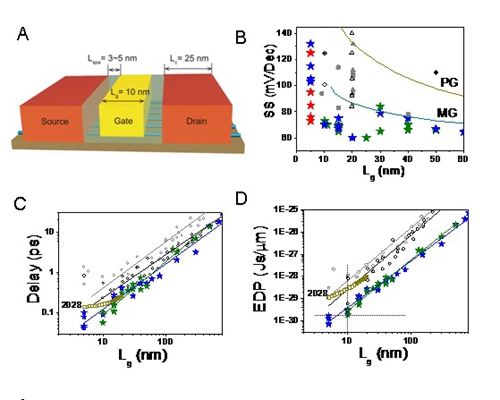

近年来,课题组通过优化器件结构和制备工艺,首次实现了栅长为10 nm的碳管顶栅CMOS场效应晶体管(对应5 nm技术节点),p型和n型器件的亚阈值摆幅均为70 mV/DEC(DEC表示倍频程);器件性能不仅远远超过已发布的所有碳管器件,并且在更低的工作电压(0.4 V)下p型和n型晶体管的工作性能均超过了目前最好的硅基CMOS器件在0.7 V电压下的性能(英特尔公司的14 nm节点);特别是碳管CMOS晶体管本征门延时仅0.062 ps,相当于14 nm硅基CMOS器件(0.22 ps)的1/3。随后,课题组进一步探索5 nm栅长(对应3 nm技术节点)的碳管,采用石墨烯作为碳管晶体管的源漏接触,有效地抑制了短沟道效应和源漏直接隧穿,从而制备出了5 nm栅长的高性能碳管晶体管,器件亚阈值摆幅达到73 mV/DEC。在此基础上,课题组全面比较了碳管CMOS器件的优势和性能潜力。研究表明,与相同栅长的硅基CMOS器件相比,碳管CMOS器件具有10倍左右的速度和动态功耗(能耗延时积)的综合优势以及更好的可缩减性。通过分析实验数据可以看出,5 nm栅长的碳管器件开关转换仅有约1个电子参与,并且门延时达到42 fs,非常接近二进制电子开关器件的极限(40 fs)——该极限由海森堡测不准原理和香农-冯诺伊曼-朗道定律所决定;也就是说,5 nm栅长的碳管晶体管已接近电子开关的物理极限。

与此同时,课题组也研究接触尺寸缩减对器件性能的影响,探索器件整体尺寸的缩减,将碳管器件的接触电极长度缩减至25 nm,在保证器件性能的前提下,实现了整体尺寸为60 nm的碳管晶体管,并且成功演示了整体长度为240 nm的碳管CMOS反相器,这是目前所实现的最小的纳米反相器电路。

该工作于2017年1月20日在线发表于《科学》(Science,链接:http://science.sciencemag.org/content/355/6322/271,DOI: 10.1126/science.aaj1628)。信息学院博士后邱晨光为第一作者,张志勇、彭练矛为共同通讯作者。研究成果不仅表明在10 nm以下的技术节点,碳纳米管CMOS器件较硅基CMOS器件具有明显优势,且有望达到由测不准原理和热力学定律所决定的二进制电子开关的性能极限,更展现出碳纳米管电子学的巨大潜力,为2020年之后的集成电路技术发展和选择提供了重要参考。

以上研究得到国家重点研发计划、重大科学研究计划、国家自然科学基金(优秀青年科学基金、创新研究群体)、北京市科技计划、北京大学“中央高校建设世界一流大学(学科)和特色发展引导专项”等资助。

信息与工程科学部

信息与工程科学部